# IGBT versus VDMOS switches in DC-to-AC inverters, some basic comparisons

Jelena Milojković, Simon Le Blond, Marko Dimitrijević and Vančo Litovski

Abstract - Renewable energy sources invariably require interfaces for power conversion, and new switches based on modern semiconductors may offer converters with improved efficiency. This study investigated properties of two contemporary voltage-controlled power transistors, and their suitability for use in DC-to-AC inverters. Namely Si IGBT and Si VDMOS were considered. These devices were implemented in a Low-Voltage Single-Phase H-Bridge based Inverter (LVSPHBI) and simulated with LTSPICE, with simulations for different levels of power delivered to a linear resistive load while keeping the DC voltage source constant. The efficiency and total harmonic distortion (THD) were used as measures of merit. The study includes frequency dependence of the efficiency and the THD for various technologies. It was found that each of the transistors has advantages from proper point of view.

Keywords – DC-to-AC inverters, IGBT, VDMOS

## I. Introduction

Due to the high impact of fossil fuels on the environment, renewable energy sources have become the most important consideration in the development of electrical power systems [1]. The output of primary renewable sources, however, are strongly dependent on microclimate conditions (wind speed, insolation), which as a consequence, lead also to variable (DC or AC) output voltage.

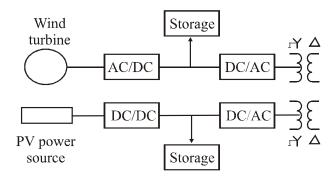

Fig. 1. Power conversion suits in two alternative-energy-source chains. Top wind energy and bottom photovoltaic energy

Jelena Milojković is with Innovation Centre of Advanced Technologies, Niš, Serbia, E-mail: jelena.milojkovic@icnt.rs Simon Le Blond is with University of Bath, United Kingdom, E-mail: s.p.leblond@bath.ac.uk

Marko Dimitrijević is with Faculty of Electronic Engineering, University of Niš, Sebia, E-mail: marko.dimitrijevic@elfak.ni.ac.rs

Vančo Litovski is independent researcher, Serbia, E-mail: vanco@elfak.ni.ac.rs

Fig. 1 depicts two "processing" chains which start with a renewable source and end with a source of stabilized (amplitude and frequency) AC voltage ready to be connected to the grid. It consists of several stages, performing conversion and inversion of the original unstabilized AC or DC voltage.

As can be seen from Fig. 1, the DC-to-AC inverter represents an unavoidable subsystem in the connection of a renewable energy source to the grid, be it micro-, smart-, or ordinary [2], [3]. This is why much attention was given to the development and design of various types of DC-to-AC inverter [4].

Within the extensive variety of converter implementations, we consider here the most common, namely, the Low-Voltage Single-Phase H-Bridge based Inverter (LVSPHBI). In particular, the device is built from voltage controlled switches, which in modern times, have replaced thyristors [5], [6].

Our intention was to collect and publicize comparative information about the behavior of LVSPHBIs using two technologies: the silicon VDMOS and the silicon IGBT. As a measure for comparison, two main metrics were used: the efficiency and the Total Harmonic Distortion (THD).

In the next section, we begin with the properties of the devices from the implementation perspective for DC-to-AC inverters. Then, results of a systematic search with responses obtained by simulation will be reported, enabling comparisons between the devices. Finally, some conclusions from this study will be drawn.

# II. MAIN PROPERTIES OF THE COMPONENTS IMPLEMENTED

In the search for fast switching devices able to handle large voltages and currents existing silicon devices the N-VDMOS (Vertical Double Diffused MOS) and the IGBT (Insulated Gate Bipolar Transistor) are frequently used, due to the fact they are voltage controlled and alike thyristors, consume low energy at the input terminal which, in addition, needs no current source.

Application of these components in low-voltage solidstate circuit breakers and comparisons of the circuit properties was reported in [7], while similar studies are reported for the implementations in single-phase low-power low-voltage T-type DC-to-AC inverters [8] where no VDMOS was taken into account.

| Туре                                            | V <sub>max</sub> (V) | T <sub>max</sub> (°C) | C <sub>ISS</sub> (pF) | C <sub>RSS</sub> (pF) | Coss<br>(pF) |

|-------------------------------------------------|----------------------|-----------------------|-----------------------|-----------------------|--------------|

| Si MOS (V <sub>DS</sub> =25 V) R5021ANX         | 600                  | 150                   | 2300                  | 70                    | 1000         |

| Si IGBT (V <sub>AK</sub> =20 V) NGTB30N135IHRWG | 1350                 | 150                   | 5290                  | 100                   | 124          |

Table 1. Power transistor's maximum voltages at the output terminal, maximum temperatures, and capacitances

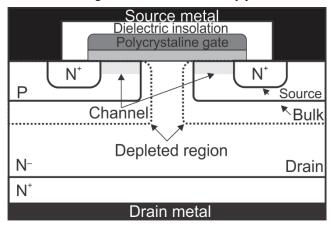

Fig. 2 shows the structure of a modern high-voltage and high-power device, specifically the cross-section of a VDMOS. Its practical implementation is in fact a complex integrated circuit containing hundreds of cells (like the one depicted) connected in parallel. To allow for high voltages a depletion region is inserted between the drain and the channel while high currents are achieved by parallelization.

Figure 2. Cross section of an enhancement type N-channel VDMOS

In this paper the following components will be used for creation of the inverter: the R5021ANX VDMOS [9]; the NGTB30N135IHRWG IGBT [10].

Table 1 depicts some of the properties of the components listed above (taken from original datasheets). Among them the maximum voltage at the output terminal is of prime importance. The components selected both have maximum voltage above 400 V which makes them well suited to the subsequent experiment.

For high-power implementation point of view (having in mind the expenses for cooling) the electronic maximum operating temperature  $(T_{\max})$  is of prime importance.

The rest of Table 1 is related to device capacitances. The influence of capacitance the transistor's responses to a pulsed input signal will be discussed briefly later on.

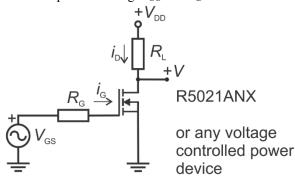

To build a realistic a picture of the behavior of the above components we will first consider their static characteristics. To that end, the simple circuit of Fig. 3 was created. It allows for graphic analysis of the output characteristic and determination of the minimum voltage for different values of the circuit parameters e.g.  $V_{\rm DD}$  and  $R_{\rm L}$ .

Figure 3. The test circuit

Some of the results obtained by LTSPICE [11] simulation are depicted in Fig. 4. In Fig. 4a we used  $V_{\rm DD}$ =50V and  $R_{\rm L}$ =5/8 Ohm. (It would be more realistic to use 8 times greater  $V_{\rm DD}$  and  $R_{\rm L}$  but the figure would not be so readable, while the conclusions would be the same.)

For a given gate voltage, (say, equal to the amplitude of the input pulse) the minimum value of the output voltage is restricted by the intersection between the load line and the proper output characteristic of the transistor, here denoted by the letters A and B. As can be seen from Fig. 4 the difference between the minimum voltages is in favor of the IGBT (denoted as Si\_IGBT) as compared to the VDMOS (denoted as Si\_MOS). Note, if 8 times larger  $V_{\rm DD}$  and  $R_{\rm L}$  were used, the upper-left end of the load line would not change, while the lower-right would move 8 times further to the right, resulting in even larger minimum voltage for the VDMOS.

The interception points A-B define the maximum swings of the output voltage and current and consequently the efficiency. Since alternating currents (AC) are considered, the larger these swings are the better.

The same effect may be observed from the pulse responses of the circuits containing the same set of transistors as listed above.

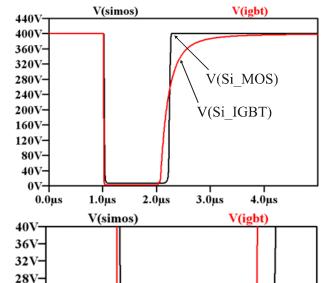

The simulation results for a 1  $\mu$ s long input impulse are depicted in Fig. 5. Fig. 5a represents the output voltage of the circuit of Fig. 3 for  $V_{\rm DD}$ =400 V and  $R_{\rm L}$ =310<sup>2</sup>/(2·5500)  $\Omega$  which will later be used for the case where required inverter output power is  $P_{\rm out}$ =5.5 kW. While the bottom of the output

E=200V.

24V-

20V-

16V

12 V· 8 V·

4V

0.5µs

$0.9 \mu s$

pulse is lower making its amplitude larger the large input capacitance of the IGBT maps to a larger delay of the rising edge of the response as compared with the VDMOS.

Fig. 4. Illustration of the value of the minimum output voltage (points A and B) for different technologies and different output powers.

In the case when larger power is required ( $P_{\text{out}}$ =10 kW) the value of the load resistor was changed to  $R_L$ =310²/(2·10⁴)  $\Omega$ . The simulation results for this case are depicted in Fig. 5b. Here only the floor of the output pulse is shown in order to emphasize the differences introduced by different technologies. For large powers the amplitude of the output pulse is reduced and so is the efficiency. This reduction, however, strongly varies across the different technologies starting with approximately 2.5 V for the case of the IGBT and ending with 13 V for the Si MOS.

## III. THE DC-TO-AC INVERTER

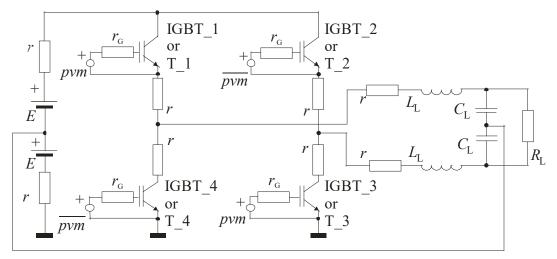

The structure of the single-phase H-bridge inverter is dual to the full-wave rectifier in the sense that the DC and AC ports are interchanged. Both, however, need a low-pass filter to eliminate the unwanted components of the output signal. Fig. 6 depicts the schematic used in this paper for the inverter implemented with IGBTs. Here in all cases

Fig. 5. Time domain responses of the circuit of Fig. 3 for different types of transistors. a) The complete pulse responses.  $R_L$ =310²/(2·5500)  $\Omega$  as (later used in the inverter simulation) and b) the floor of the output pulses highlighted.  $R_L$ =310²/(2·10⁴)  $\Omega$  as (later used in the inverter simulation). The value of  $r_G$  corresponds to the value used for simulation later

1.3 µs

V(Si MOS)

V(Si IGBT)

1.7µs

2.1µs

2.5µs

The pvm signal is obtained from a subsystem (not shown) which generates a pulse-width-modulated signal [12], [13]. It is characterized by two quantities: the frequency,  $f_s$ , of the triangular waveform set against the 50 Hz sinusoid comparator to produce a pulse train, and the index representing the quotient of the amplitudes of the sinusoid and the triangular waveform,  $M_a$ . The latter is the parameter that determines the pulse train and thus is the main controlling parameter allowing adjustments of the amplitude of the output voltage. In reality, the connection of the pwm signal and its complement to the input terminals of the switching devices is quite complex, but for the purpose of this study, it may be satisfactorily approximated with a simple resistor,  $r_G$ .

# IV. SIMULATION RESULTS

The input (battery) power was calculated as follows

$$P_{\text{bat}} = 2 \cdot E \cdot I_{\text{bat}} \tag{1}$$

Fig. 6. The schematic used as a AC-to-DC inverter.

where  $I_{\text{bat}}$  is the DC component of the battery current produced (after transient simulation of the inverter) by the [.four] command in LTSPICE. On the other side, the AC power delivered to the load was calculated by

$$P_{\text{load}} = V_{\text{load}} \cdot I_{\text{load}} / 2 \tag{2}$$

where  $V_{\rm load}$  and  $I_{\rm load}$  represent the amplitudes of the load voltage and current, respectively, which were produced (after transient simulation of the inverter) by the [.four] command of LTSPICE.

The efficiency was obtained by the following expression

$$\eta = 100 \cdot P_{\text{load}} / P_{\text{bat}} \left[\%\right] \tag{3}$$

(To make results clearer, in the next section, the efficiency as a decimal is used, i.e.  $\eta/100$ ).

To produce the dependences of the efficiency and the *THD* on the power delivered to the load, repetitive simulations of the circuit of Fig. 6 were performed. Two quantities were changed to obtain the drawings for a given value of the load power. Namely, the load resistance was calculated first to be  $R_{\rm L}=310^2/(2\cdot P_{\rm load})$ , and then the circuit was repeatedly simulated with various values of  $M_{\rm a}$  until the output voltage became almost equal (but slightly larger) to 310 V.

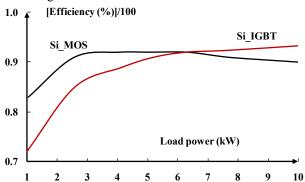

The results for efficiency are depicted in Fig. 7. When considering Fig. 7 and Fig. 5b simultaneously, one must also recall that during the inverter's on state, two transistors are connected in series thus reducing the amplitude of the output voltage by a value twice as large as that depicted in Fig. 5b (or Fig. 4).

From the perspective of efficiency, based on Fig. 7, at low powers (as depicted in Fig. 4b) the VDMOS is advantageous as compared with the IGBT based inverter. Whilst its efficiency suffers at low powers, its low value of the minimum voltage at high currents, as discussed above, allows for high efficiency when high power is required.

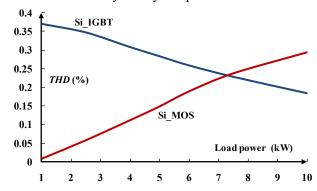

As described in detail in [14] the harmonic distortions are one of the most important indices of the quality of the delivered electrical power. Here we performed Fourier

analysis, using LTSPICE, up to the 250<sup>th</sup> harmonic of the power frequency i.e. up to 12.5 kHz. Since linear resistive load was considered only, the results given below for the load voltage are the same for the load current.

Fig. 7. Efficiency as a function of the power frequency power delivered to the load for different technologies

The results are depicted in Fig. 8. The distortions introduced by the inverter are very small. For example, for the case of IGBT based inverter at  $P_{\rm load}$ =2.5 kW the THD is equal to 0.35% (almost the largest value). The VDMOS based inverter introduces even smaller distortions which decrease dramatically at very low powers.

Fig. 8. *THD* as a function of the power frequency power delivered to the load for different technologies

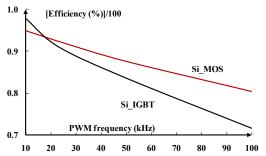

Finally, the dependence of the inverter's properties as a function of the frequency  $f_s$  used in the pwm signal generator is of interest. At low frequencies, irritating audible noise is frequently produced by this type of equipment due to the nonlinearities that generate harmonics. For this reason, higher frequencies are preferred. The efficiency and the distortions at higher frequencies are therefore of interest.

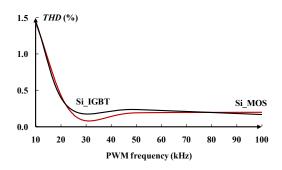

Fig. 9 depicts the dependence of the efficiency of both types of inverter as a function of the frequency used in the PWM signal generator. The general conclusion is that the efficiency decreases with the rise of  $f_{\rm s}$ . Given the trend suggested by the curve, it could be argued the Si\_MOS based inverter is preferable at high frequencies. From the perspective of distortion, as can be seen from Fig. 10, at high frequencies both the IGBT based and VDMOS based inverters perform very well.

Fig. 9. Efficiency as a function of the frequency  $f_s$  used in the PWM subsystem for different technologies

Fig. 10. *THD* as a function of the frequency  $f_s$  used in the PWM subsystem for different technologies

#### V. CONCLUSION

The DC-to-AC inverter is a ubiquitous subsystem of modern renewable alternative energy sources. Its properties map themselves directly into the characteristics of the waveforms delivered to the load (or the grid), thus the device deserves much attention in the search for improvement. This study investigated the advantages and disadvantages of using existing Si based voltage controlled switching devices in a conventional single-phase single-triangle PWM H-bridge inverter. The efficiency and the *THD* were used as measures of merit. LTSPICE simulation was used for all results reported here. Based on the results obtained, we may conclude that the VDMOS and the IGBT have application

niches of their own in which they perform better.

#### **ACKNOWLEDGEMENT**

This research was partly funded by The Ministry of Education and Science of Republic of Serbia under contract No. TR32004.

# REFERENCES

- [1] Michaelides, E., "Alternative energy sources", Springer Verlag, Berlin, Germany, 2012.

- [2] Keyhani, A., "Design of Smart Power Grid Renewable Energy Systems", John Wiley and Sons, Inc, Hoboken, N.J., 2011

- [3] Li, F., Qiao, W., Sun, H., Wan, H., Wang, J., Xia, Y., Xu, Z., and Zhang, P., "Smart Transmission Grid: Vision and Framework", IEEE Trans. on Smart Grid, Vol. 1, No. 2, 2010, pp. 168-177.

- [4] Wang, X, Guerrero, J. M., Blaabjerg, F, and Chen, Z, "A Review of Power Electronics Based Microgrids", Int. J. of Power Electronics, Vol. 12, No.1, 2012, pp.181-192.

- [5] B.Burger and D. Kranzer, "Extreme high efficiency PV-power converters," in Proc. Power Electron. Appl. Conf., 2009, pp. 1–13.

- [6] Dapkus II, D.A., "Using MOS-Gated Power Transistor in AC Switch Applications", International Rectifier, Technical paper DT 94-5, www.irf.com, last visited December 18, 2015.

- [7] Milojković, J., Litovski, V., and Le Blond, S., "Low-Voltage Circuit Breakers Based on WBG Solid-State Devices", J. of Circuits, Systems and Computers, Vol. 27, No. 2, February 2018 [19 pages]https://doi.org/10.1142/S0218126618500202.

- [8] Gurpinar, E. and Castellazzi, A., "Single phase T-type inverter performance benchmark using Si IGBTs, SiC MOSFETs and GaN HEMTs", IEEE Trans. on Power Electronics, Vol. 31, No. 10, 2016, pp. 7148-7160.

- [9] http://www.rohm.com/web/eu/search/parametric/-/search/MOSFETs?gclid=CO3M5abH5cgCFQSVGwodJqUJ8w, last visited November 2017.

- [10] http://www.onsemi.com/pub/Collateral/NGTB30N 135IHR-D.PDF, last visited November 2017.

- [11] http://www.linear.com/solutions/ltspice, last visited November 2017.

- [12] Lai, Z., and Smedley, K. M., "A General Constant-Frequency Pulsewidth Modulator and Its Applications", IEEE Trans. on Circuits and Systems-I: Fundamental Theory and Applications, Vol. 45, No. 4, April 1998, pp. 386-396.

- [13] Hobraiche, J., Vilain, J.-P., Macret, P., and Patin, N., "A New PWM Strategy to Reduce the Inverter Input Current Ripples", IEEE Trans. on Power Electronics, Vol. 24, No. 1, January 2009, pp. 172-180.

- [14] Heydt, G. T., "Electric power quality", Stars and Circle Publications, West Lafayette, Indiana, USA, 1991. and Optimization", Chapman and Hall, London, 1997.